- 全部

- 默认排序

随着数字电路应用领域越来越多,可编程逻辑器件(Programma Logic Device,PLD)在其带动下也成为大火的电子器件之一,这也促使了PLD芯片制造工艺的日益完善,所以我们接下来将盘点可编程逻辑器件PLD芯片制造工艺。可编程逻辑

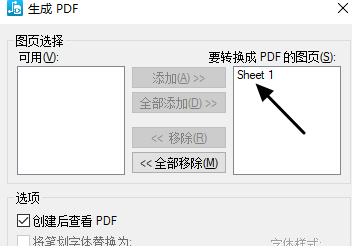

Logic设计原理图后,可以把原理图以PDF的形式输出,方便学安装软件的用户对原理图进行查阅。1)执行菜单命令“文件”→“生成PDF”进入“文件创建PDF”界面,在“文件名”栏填入文件名,指定其路径保存路径,如图4-65所示。图4-65 指

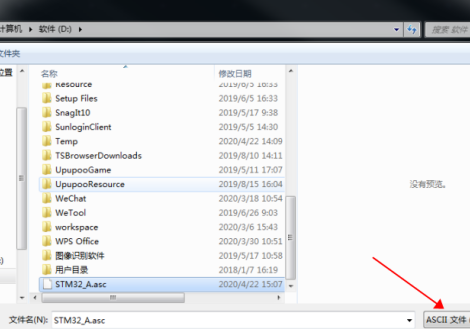

PADS Layout导入网表,即将原理图与PCB进行同步,具体步骤可参考“4.6.1 PADS Logic与layout同步操作”内容。除了导入Logic原理图文件,还可将Orcad原理图导出的ASC文件导入到Layout内。1)执行菜单

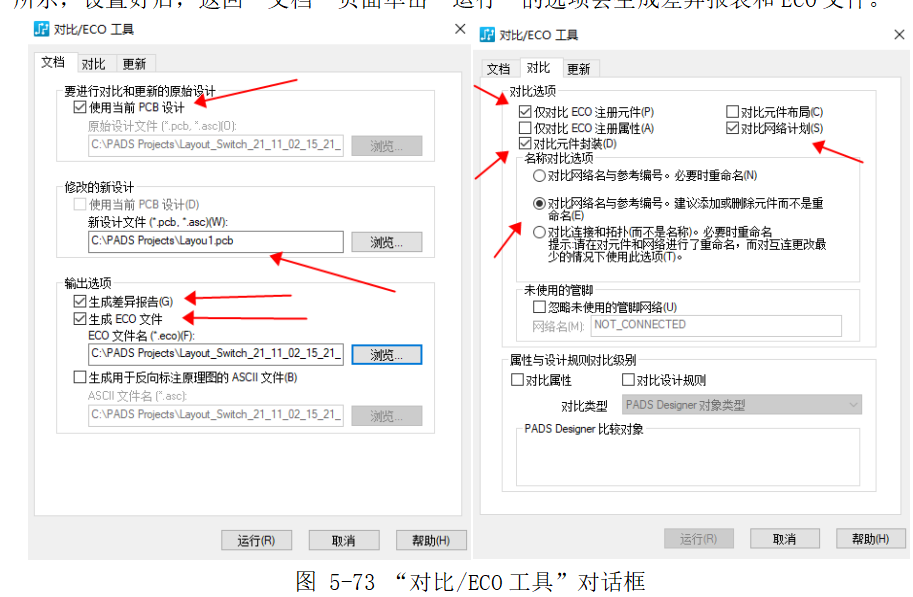

若原理图非Logic格式,是其他软件生成的.ASC文件导入,设计中有更改,需要更新PCB,则可利用ECO网络对比功能,进行PCB的更新。1)执行菜单命令“工具-对比/ECO”,如图5-73所示。将当前正在设计的PCB文件和更新中的PCB对比

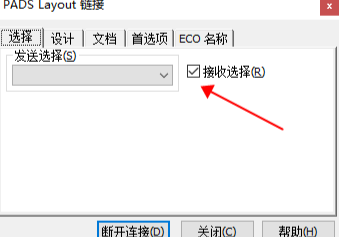

布局时一般需要与原理图同步,进行协作处理,提高布局效率。可同时打开Logic格式原理图与Layout格式PCB文件,在Logic内执行“工具-Pads Layout”命令,然后设置“选择”界面,与原理图同步的PCB须检查,以防文件不对应,一

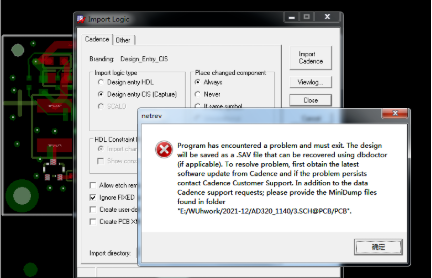

Allegro在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种解决办法:1、当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单

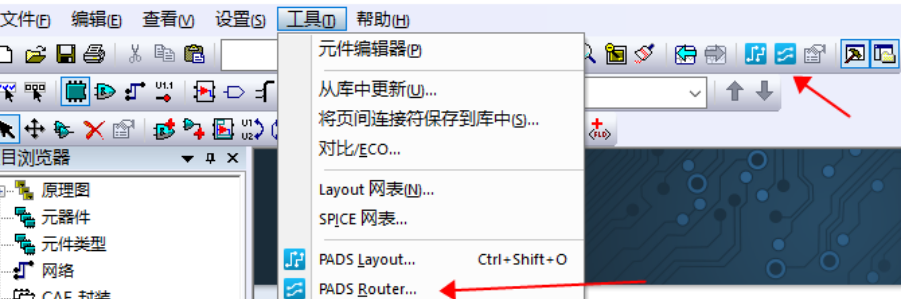

在Logic组件中,既可以和Layout组件同步设计,也可以与Router组件同步,在Logic组件中执行“工具-Pads Router”,可将Logic与Router进行同步,执行此操作时建议不要打开多个设计,以免系统同步错文件。如图6-

第一步,在Logic界面中,执行菜单命令“工具-选项”,如图1所示。第二步,弹出的“选项”对话框中,点击“设计”分栏,如图2所示。对应设计分栏的对话框中找到“图页”设置界面,在其“图页边界线”选项旁点击“选择”选项,如图3所示。图1“选项”

第一步,执行菜单命令“工具-选项”,如图1所示。第二步,弹出的“选项”对话框中,点击左分栏中“常规”选项,如图2所示。在展开的常规界面中,找到“光标”设置,点击样式中的下滑栏存在以下选项,如图4所示,按照自己的设计进行勾选。如果设计存在需要

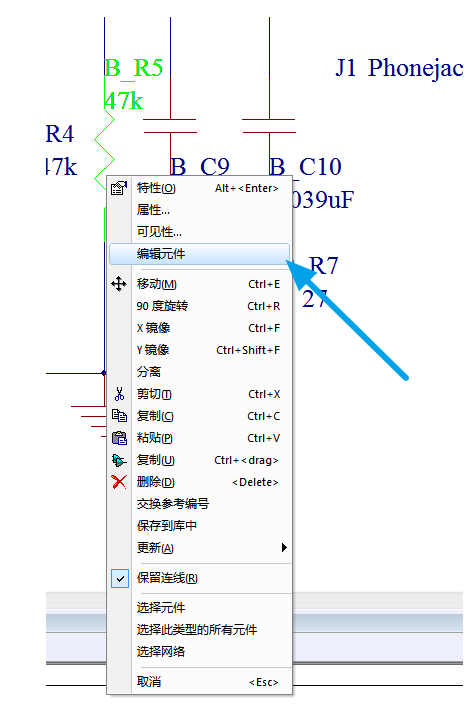

PADS Logic中单个器件的PCB封装应该怎么处理呢?第一步,单击要匹配的器件,然后右击选择“编辑元件”,编辑该元件属性,如图1所示: 第二步,在弹出元器件属性中,执行菜单命令“编辑-元件类

扫码关注

扫码关注